DDR 测试可最大限度地提高 DDR 从初始上电启动到验证的运行效率

正确的示波器工具可支持 DDR 和 LPDDR 电气验证、JEDEC 合规性测试以及在设计的多个阶段进行调试。Teledyne LeCroy 可缩短调试时间,并帮助您找到通常被忽视的错误。

DDR 调试工具包特性和功能

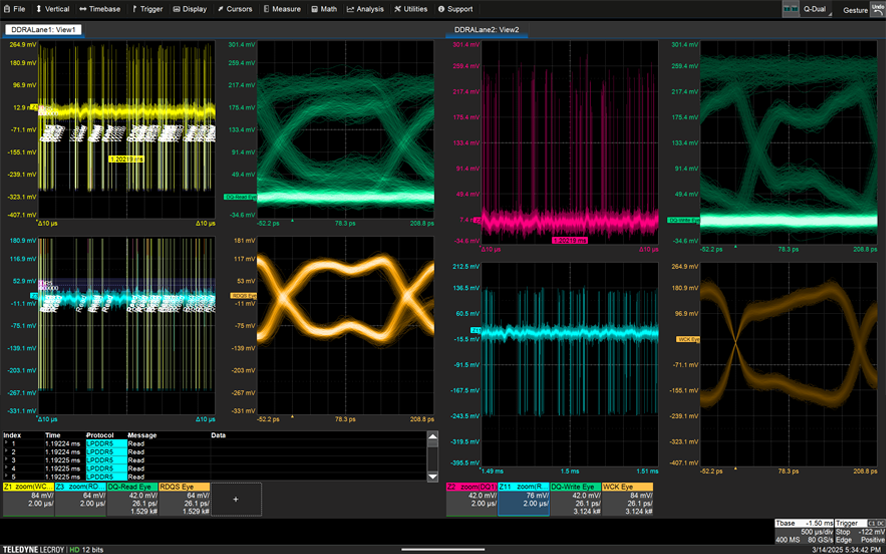

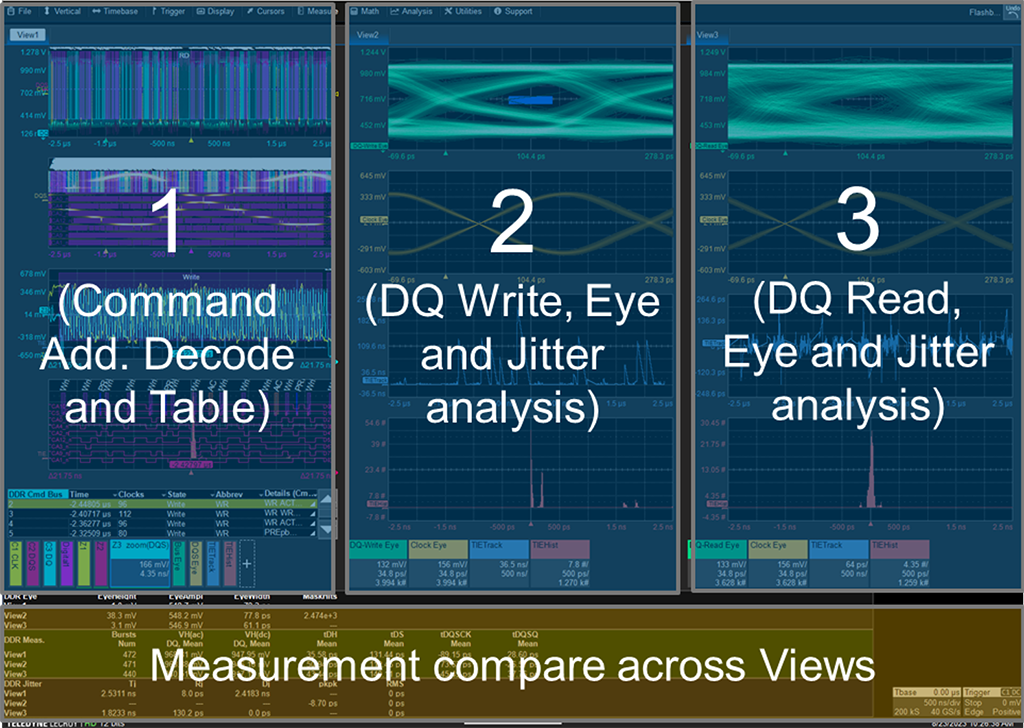

DDR 调试工具包为用户提供了按需构建测试场景的能力,支持多个分析区域的设置,可对命令总线进行解码与触发,并通过符合 JEDEC 标准的眼图、模版测试以及 DDR 专用测量功能,深入优化设计阶段。

多场景查看

- 布局4种独特的测试场景

- 之前vs. 之后的信号比较

- 去嵌vs. 原始

- 读写时钟比较

- 测量比较

眼图、模板测试和 JEDEC 特定测量

- 交互式用户工具包

- 眼图和模板测试

- JEDEC 或定制眼图模版

- 眼图分析的“Failures”

- LPDDR 和 DDR 特定测量

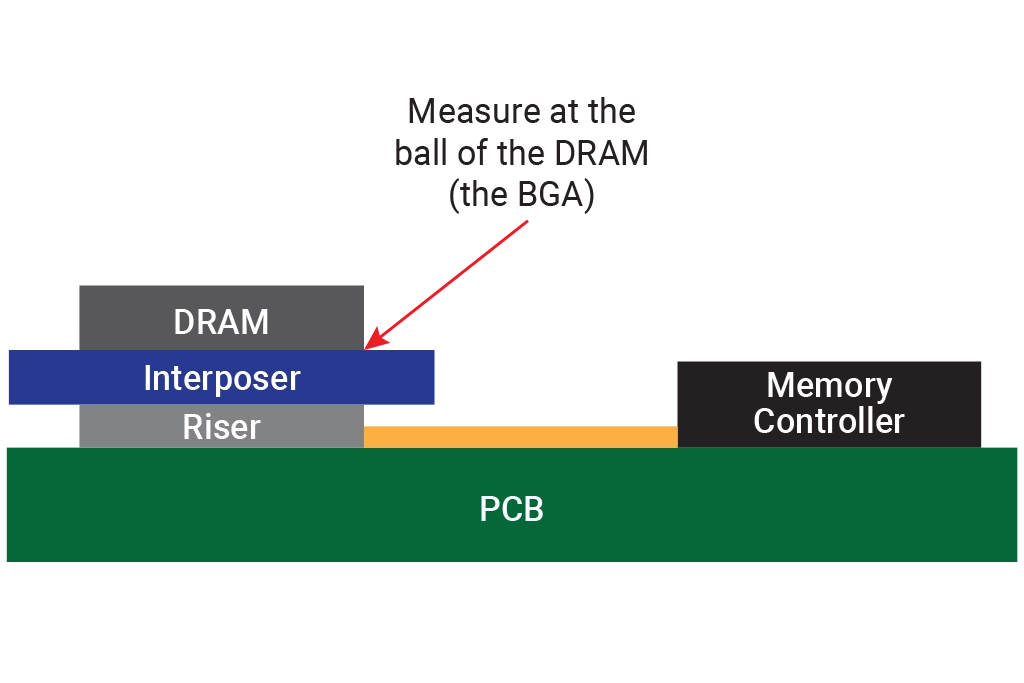

全面的 DDR 内存测试,满足 JEDEC DDR 合规性和调试要求

实现LPDDR 和 DDR 合规性测试自动化,从而缩短测试时间并减少错误。使用共享测试设置,快速在 DDR 调试工具包根本原因故障分析和合规性测试之间切换。

JEDEC DDR 合规性测试的全面自动化覆盖

- 通过一致的设置和可重复使用的配置实现自动化测试

- 验证 DRAM Ball的关键电气和时序参数,生成眼图

- 以 HTML 或 PDF 格式导出结果,以便于共享和分析

- QPHY2-DDR5-SYS

- QPHY2-LPDDR5

- QPHY-DDR3(DDR3/3L/LPDDR3)

- QPHY-DDR4 (DDR4/LPDDR4/4X)

从合规性测试快速过渡到 DDR 调试工具包设置

- 在 DDR 调试工具包中配置所有必要的 DDR 测试设置参数

- 快速确定优化的测试设置,以获得最佳的 DDR 信号保真度

- 将 DDR 调试工具包测试设置复制到 QualiPHY 2 合规性测试选项可节省设置时间

使用 QualiPHY 2 在极短的时间内完成验证和合规性测试

- 简化的测试界面——易于理解和操作

- 随时随地按时测试——在实验室内或离线(实验室外)

- 从 DDR 调试工具包共享测试设置

推荐用于 DDR 测试的 DDR 示波器、探头和软件

请参考下面的标签和链接,了解更多有关用于 DDR 测试的 Teledyne LeCroy 产品,以及合作伙伴的interposers或测试服务的信息。

资源中心

| 姓名 | |

|---|---|

LPDDR5 数据表 QualiPHY 2 (QPHY2-LPDDR5) 数据表概述了测试功能、订购信息以及更多对内存设计感兴趣的工程师的信息。 | 产品规格书 |

DDR5 数据表 测试 DDR5 系统级设计的所有阶段(在 BGA 处)。 本数据表概述了通过 QualiPHY 自动合规性测试实现早期开启的工具。 执行 JEDEC 概述的调试和合规性测量。 了解所需设备和订购信息。 | 产品规格书 |

DDR4/LPDDR4/LPDDR4X 数据表 QualiPHY (QPHY-DDR4) 数据表为对内存设计感兴趣的工程师概述了测试功能、订购信息等。 | 产品规格书 |

DDR3/DDR3L/LPDDR3 数据表 QualiPHY (QPHY-DDR3) 数据表为对内存设计感兴趣的工程师概述了测试功能、订购信息等。 | 产品规格书 |

DDR2 数据表 QualiPHY (QPHY-DDR2) 数据表为对内存设计感兴趣的工程师概述了测试功能、订购信息等。 | 产品规格书 |

LPDDR2 数据表 QualiPHY (QPHY-LPDDR2) 数据表为对存储器设计感兴趣的工程师概述了测试功能、订购信息等。 | 产品规格书 |

DDR 和 LPDDR 调试工具包数据表 LPDDR 和 DDR 调试支持 DDR 2/3/4/5 和 LPDDR2/3/4/4X/5/5X 并允许进行深度故障排除。 | 产品规格书 |

成为 DDR 内存物理层测试专家,进行 DDR 调试、合规性和验证

与 Teledyne LeCroy 一起参加这个大师级网络研讨会系列,了解使用示波器进行 DDR 测试的基础知识,包括常见的测试准备和挑战、合规性测试工具和调试测试工具之间的差异,以及提高 DDR 验证效率和应用正确方法的实用技巧和技术。调试工具。

全部注册在本次网络研讨会中,我们将全面介绍 DDR 接口以及测试过程中遇到的挑战。我们将重点讲解如何区分验证测试和合规性测试要求,以及如何准备 DDR 内存测试。

本次网络研讨会将详细介绍如何解决实际应用中影响 DDR 测量能力的探测和连接问题。我们将提供一些示例,说明哪些操作可以做,哪些操作不能做,并回顾一份预合规测试清单。

在本次网络研讨会中,我们将提供使用调试工具克服 DDR 测试挑战的实用建议。主题包括实际的 DDR 调试示例,例如逻辑、焊接和电源问题、DDR 读/写分离、眼图形成以及如何解决丢失的时钟周期。我们还将讨论 DDR 眼图、多种场景下的抖动、基于硬件的读写分离以及虚拟探测技术。

在本次网络研讨会中,我们将详细介绍 JEDEC DDR5 和 LPDDR5 规范和测试要求与以前版本的 DDR 有何不同,以及如何优化 DDR5 和 LPDDR5 内存测试。

| 姓名 | |

|---|---|

DDR4/LPDDR4/LPDDR4X 使用说明书 QualiPHY (QPHY-DDR4) 说明手册,分步说明如何操作和测试 DDR4、LPDDR4、LPDDR4X DRAM 标准。 | 使用指导手册 |

DDR3/DDR3L/LPDDR3 使用说明书 QualiPHY(QPHY-DDR3)使用说明书,逐步指导如何操作和测试 DDR3、DDR3L、LPDDR3 DRAM 标准。 | 使用指导手册 |

DDR 和 LPDDR 调试工具包使用手册 DDR 调试支持所有 DDR 2/3/4/5 和 LPDDR2/3/4/4X/5 并允许解决棘手的问题。 本手册可帮助您充分发挥该工具的潜力 | 使用指导手册 |

DDR2使用说明书 QualiPHY (QPHY-DDR2) 说明手册,提供有关如何操作和测试 DDR2 DRAM 标准的分步说明。 | 使用指导手册 |

LPDDR2 使用说明书 QualiPHY (QPHY-LPDDR2) 说明手册,提供有关如何操作和测试 LPDDR2 DRAM 标准的分步说明。 | 使用指导手册 |

QPHY2-DDR5-SYS 使用说明书 QualiPHY 2 (QPHY2-DDR5-SYS) 使用说明书,提供有关如何操作和测试 DDR5 标准的逐步说明。 | 使用指导手册 |

QPHY2-LPDDR5 使用说明书 QualiPHY 2 (QPHY2-LPDDR5) 使用说明书,提供有关如何操作和测试 LPDDR5 标准的逐步说明。 | 使用指导手册 |