80G视频

分析仪/发生器

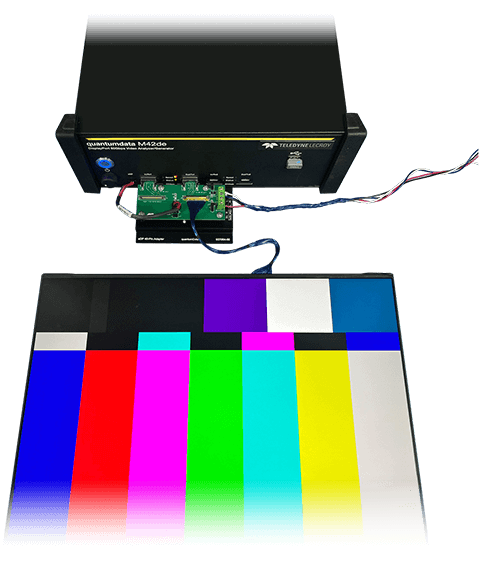

Quantumdata M42de 视频分析仪/信号发生器为 DisplayPort 2.1 的视频、音频和协议层测试提供了前所未有的功能性和一致性测试组合。

M42de 现已增强对嵌入式 DisplayPort(eDP)的支持,新增功能包括:ALPM、无辅助信号的 ALPM、PSR1/PSR2、备用扰码种子以及 Tx 背光控制。它在所有 VESA 推荐的 eDP 链路速率上均表现出色,可进行快速链路训练,是测试信号源和面板的首选。此外,全新的 30 针和 40 针 eDP 适配器简化了 eDP 1.5a 信号源和接收设备与 M42de 平台的连接,确保了准确性和便捷性。

源链路层一致性测试

DP 源链路层一致性测试选件非常适合在提交给认证测试中心之前预测试支持 HBR3 或 UHBR 的设备。 预测试被认为是确保认证过程顺利进行的关键步骤。 可选的一致性测试包允许用户查看详细结果并帮助查明故障的原因。 AUX 通道traces也在链路层测试期间保存,以提供 AUX 交互过程的记录。

接收端链路层和 EDID 一致性测试

DP 接收端 EDID/DisplayID 和链路层一致性测试选件完全支持 DP 1.4 认证和不断增加的 DP 2.1 测试案例。 链路层 CTS 测试包涵盖数十个测试用例和数百个验证用例,是工程验证测试工作的基础。 通过对包括训练、前向纠错 (FEC)、电源管理和多字节 AUX 交互在内的关键功能进行基本测试,该基础包是全面测试范围的基本配置。

LTTPR 源、接收器和定时器一致性测试

Quantumdata M42de 提供链路训练可调物理中继器 (LTTPR) 一致性的一键式自动化测试。 现在,通过对支持 HBR3 和 UHBR 的 DisplayPort 源、接收端和定时器设备进行特定测试,M42de 可以模拟真实的 LTTPR 网络行为,以验证源可以在透明和非透明模式下正确配置和链接序列。 自动生成简单的通过/失败报告并捕获详细的 AUX 日志,这对于了解时钟数据切换阶段、均衡或通道间对齐期间的问题非常有价值的。

qdPrime 测试套件提供了一个巨大的库 quantumdata 专有测试旨在验证 DisplayPort 功能以及源和接收器的互操作性。此可选功能系统地测试通道宽度、链路速率、时序、刷新率、色彩空间和位深度的不同组合,以确保设备在 DisplayPort 2.1 生态系统中正常运行。每个单独的测试都会生成带有详细日志的通过/失败结果,以提供设备互操作性的可重复快照。

| 姓名 | |

|---|---|

使用 DisplayPort 被动监控解决现实世界的互操作性问题 Teledyne LeCroy 的 TAP4™ 用于完全被动监控 DP 协议总线的专有技术提供了一个非侵入式分接头,允许查看主链路和 AUX 通道流量,以便调试真实 DP 2.1 设备之间的互操作性问题。 | 白皮书 |

qdPrime:全面的 DisplayPort2.1 自动化测试覆盖范围 | 白皮书 |

qdPrime 自动化测试覆盖率:入门 Teledyne LeCroy qdPrime 测试套件概述。 | 应用笔记 |

quantumdata eDP 适配器数据表 | 产品规格书 |

运用 quantumdata M42de 传输连续测试模式 本技术简介说明了如何使用 M42de 通过使用 Tx 端口传输各种测试模式来表征有源电缆。 | 应用笔记 |

这项全面的技术培训将详细介绍 eDP 协议层的功能、实现和测试细节。了解 eDP 为何迅速取代 LVDS 成为嵌入式显示应用的最佳技术。

参加本次网络研讨会,了解有关 DisplayPort 2.1 面板重播模式的详细培训,并探索最新的节能功能和协议行为,重点是测试和验证面板重播及其前身电源自刷新 2 (PSR2) 实现。

参加此技术网络研讨会,了解有关最新 DisplayPort 2.1 一致性测试规范 (CTS) 的完整简介。

该网络研讨会描述了 Teledyne LeCroy 应用程序编程接口 (API) 用于控制 quantumdata M42d/M41d 和 980 系列 DisplayPort 测试仪器。

该网络研讨会介绍了 DisplayPort 2.0 链路层协议在 UHBR 网络中与 LTTPR 设备的操作,以及如何测试支持 LTTPR 的设备的合规性。

尺寸和重量 | 高度:3.44 厘米(8.74 英寸)宽度:9.57 厘米(24.30 英寸)深度:10.94 厘米(27.79 英寸) |

连接器类型 | HDMI连接器:Out/Tx HDMI A 型;2 类。用于连接高级测试平台 GUI 的外部显示器 |

电源要求 | 100-240 伏交流电,50-60 赫兹,200 瓦 |

支持的数据速率 | 1.62、2.7、5.4 通道时为 8.1、1、2 和 4Gb/s; 10 通道 13.5、20、4Gb/s |

工作温度 | 32 至 104 (华氏度);0 至 40 (摄氏度) |

版本 | DP 2.1 |

可机架安装 | 2 RU 安装在 19 英寸机架中,带安装支架(已提供) |

命令行控制 | 以太网(RJ-45)用于外部 GUI 和 telnet。 |

内存 | 8 GB |

支持的协议 | DisplayPort、带 FEC、HDCP、MST 的显示流压缩 (DSC) |

这个 quantumdata eDP-to-DP 适配器利用 I-PEX VS 系列连接器,允许将嵌入式 DisplayPort 1.5a 源设备和接收设备连接到 M42de 分析仪/发生器平台。eDP 适配器有 30 针和 40 针两种配置,可直接连接到 M42de 测试平台上的标准全尺寸 DP 插座(如图所示)。适配器支持高达 HBR3 的链路速率,还提供集成背光通道和外部直流电源连接器,用于驱动 eDP 面板。